Compatibilities with 16-Bit dsPIC architecture:

- Pinout

- Software

- Peripherals

- Development Tools

dsPIC DSC Architecture

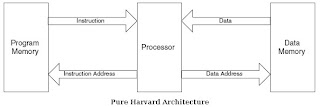

In a pure Harvard architecture has separate memory areas for program instructions and data. These two busses(instruction & Data) are completely separate, with no way to pass data between them. The CPU fetches instructions on the program memory bus and fetches data on data memory bus.

The dsPIC DSC employs a modified Harvard architecture. A modified Harvard architecture in dsPIC, has separate program memory and two data memory buses. This allows the processor to simultaneously fetch both an instruction and the data(sampled data and coefficient).

A Harvard Architecture allows to fetch single data value in one cycle. In the digital signal processing applications, it require to fetch the data fast for faster processing. For signal processing to data values are required sampled data and a coefficient by which it will be multiplied. To achieve this, the modified Harvard architecture supports three busses: one to fetch the instructions(the program memory bus) and two to fetch associated data values (often referred to in the literature as the X- and the Y-memory busses).

This allows true single cycle operation, effectively doubling system throughput when compared to a pure Harvard architecture running at the same speed.

A pure Harvard memory architecture and A Modified Harvard architecture.

No comments:

Post a Comment